# Intel® TDX Connect TEE-IO Device Guide

February 2023

#### **Disclaimers**

# **Disclaimers**

Intel Corporation ("Intel") provides these materials as-is, with no express or implied warranties.

All products, dates, and figures specified are preliminary, based on current expectations, and are subject to change without notice. Intel does not guarantee the availability of these interfaces in any future product. Contact your Intel representative to obtain the latest Intel product specifications and roadmaps.

The products described might contain design defects or errors known as errata, which might cause the product to deviate from published specifications. Current, characterized errata are available on request.

Intel technologies might require enabled hardware, software, or service activation. Some results have been estimated or simulated. Your costs and results might vary.

No product or component can be absolutely secure.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein.

No license (express, implied, by estoppel, or otherwise) to any intellectual-property rights is granted by this document.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice.

Copies of documents that have an order number and are referenced in this document or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting <u>http://www.intel.com/design/literature.htm.</u>

© Intel Corporation, 2023. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands might be claimed as the property of others.

## Table of Contents

# **Table of Contents**

| Di  | sclaimers                                 | 2  |

|-----|-------------------------------------------|----|

| Та  | able of Contents                          | 3  |

| Int | troduction and Scope                      | 6  |

|     | Glossary                                  | 8  |

| 1   | TEE-IO Device Architecture Overview       | 10 |

|     | TEE-IO Security Model                     | 10 |

|     | Security Model for the Device             | 11 |

|     | Implementing TEE-IO Device Stack          | 11 |

|     | Secure Device Interface Lifecycle Example | 12 |

| 2   | TEE-IO Software Stack                     | 15 |

|     | Software Stack Overview                   | 15 |

|     | Device Communication (DOE)                | 16 |

|     | Device Attestation (SPDM)                 | 16 |

|     | Software Secure Communication (SPDM)      | 17 |

|     | Link Encryption Key Management (IDE_KM)   | 18 |

|     | Device Interface Management (TDISP)       | 19 |

|     | Implementation Reference                  | 21 |

|     | SPDM software stack                       | 21 |

|     | IDE_KM software stack                     | 22 |

|     | TDISP software stack                      | 22 |

| 3   | TEE-IO Hardware Stack                     | 24 |

|     | IDE Stream                                | 24 |

|     | IDE Stream Precedence                     | 27 |

|     | TEE Limited Stream                        | 27 |

|     | Partial Header Encryption                 | 27 |

|     | TDI TLP Rule                              | 28 |

|     | TDI as Completer                          |    |

|     | TDI as Requester                          |    |

|     | ATS Rule                                  | 34 |

|     | Peer to Peer (P2P)                        |    |

# intel.

## Table of Contents

| TDISP Interoperability with PCIe Capabilities   |    |

|-------------------------------------------------|----|

| MSI-X                                           |    |

| ATS                                             |    |

| Direct P2P                                      |    |

| PASID                                           |    |

| LNR                                             |    |

| TPH                                             |    |

| 4 Device Security Architecture                  |    |

| Resource Isolation and Protection               |    |

| Address Translation                             |    |

| Device Resource                                 |    |

| Device Identity and Measurement Reporting       |    |

| Device Firmware Resilience                      | 40 |

| Runtime Firmware Update                         | 40 |

| Secure Interconnects                            | 42 |

| Device Attached Memory                          | 42 |

| TDI Security                                    | 42 |

| Data Integrity Errors                           | 42 |

| Debug Modes                                     | 43 |

| Device Debug Interface                          | 43 |

| Device Reset                                    | 43 |

| Conventional Reset                              | 43 |

| Function Level Reset (FLR)                      | 44 |

| Timing                                          | 44 |

| Error Handling                                  | 45 |

| Error Trigger                                   | 45 |

| Error Notification                              | 48 |

| Error Recovery                                  |    |

| 5 Summary                                       |    |

| Appendix A: Intel® TDX Connect Interoperability | 53 |

| TDX Connect Software Interoperability           | 53 |

# intel

# Table of Contents

| DOE                                                   | 53 |

|-------------------------------------------------------|----|

| SPDM                                                  | 54 |

| IDE_KM                                                | 55 |

| TDISP                                                 | 56 |

| TDX Connect Hardware Interoperability                 | 57 |

| IDE Stream                                            | 57 |

| TDISP                                                 | 59 |

| Appendix B: Secure Device Interface Lifecycle Example | 66 |

| SPDM Management                                       | 66 |

| SPDM Session Setup                                    | 66 |

| SPDM Session Termination                              | 66 |

| SPDM Session Heartbeat                                | 67 |

| SPDM Session Key Update                               | 67 |

| Device Information Recollection                       | 67 |

| IDE Stream Management                                 | 68 |

| IDE Stream Setup                                      | 68 |

| IDE Stream Stop                                       | 69 |

| IDE Stream Key Refresh                                | 70 |

| TDI Lifecycle Management                              | 71 |

| TDI Assignment                                        | 71 |

| TDI Teardown                                          | 73 |

| References                                            | 74 |

| Standards                                             | 74 |

| Web Resources                                         | 76 |

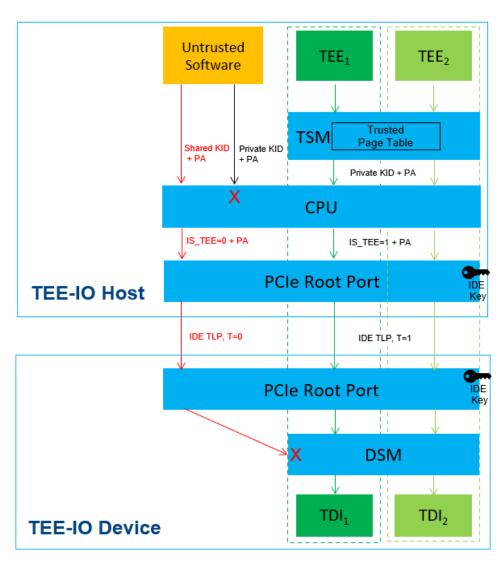

In the computer industry, hardware-based trusted execution environments (TEEs) are used to provide the confidential computing environment. In this document, such TEEs are referred to as Trusted Execution Environment VMs (TVMs) to distinguish them from traditional virtual machines (VMs). Today, multiple CPU vendors such as Intel, AMD, ARM, and RISC-V already published the solution to address the need based upon the new capability in the host CPU.

In order to achieve high performance in the data center, the host CPU may offload some workload to the device, such as Hardware Security Module (HSM) for crypto accelerating, Graphic Processing Unit (GPU) for AI processing, and Smart Network Interface Card (NIC) for network processing. In this case, the confidential computing environment is extended from the TVM to a portion of a device (TEE Device Interface, also known as TDI).

The TDI could be a Physical function (PF), a Virtual function (VF), or an Assignable Device Interface (ADI). To support such functions, the industry standard groups, such as PCI-SIG and Compute Express Link (CXL) Consortium, defined the new standard to support the use case, including Integrity and Data Encryption (IDE) and TEE Device Interface Security Protocol (TDISP).

In a host environment, we use TEE security manager (TSM) to indicate the logic Trust Computing Base (TCB) component to enforce the security policy. The TSM could be inside of a TVM, or the TSM could be a component outside of the TVM and trusted by the TVM.

Inside the device, we use Device Security Manager (DSM) to indicate the logical TCB component that enforces the security policy. The TSM should set up a secure management channel with the DSM to get the device information and manage the device interface. The TSM and DSM may also negotiate the encryption key for secure communication.

# intel.

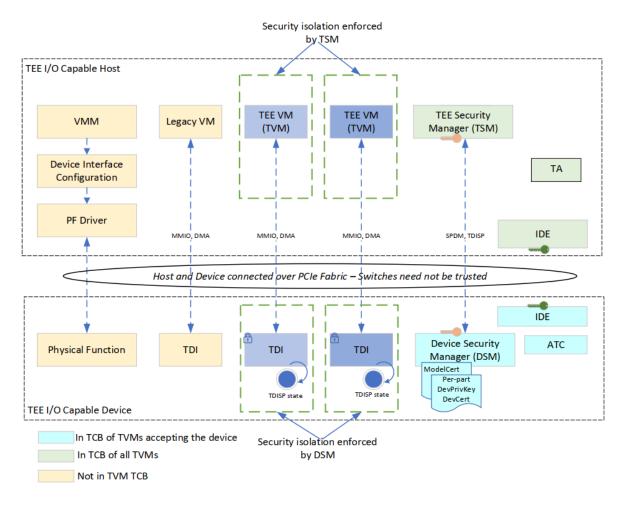

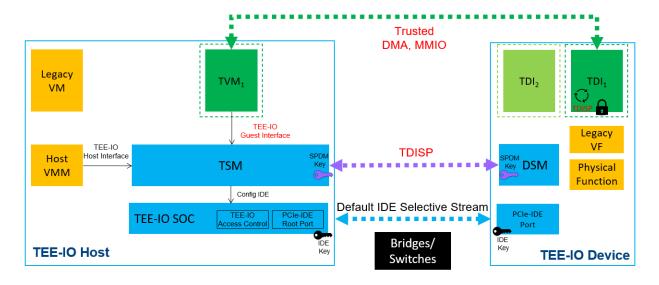

#### Figure 0-1: TEE-IO Component Conceptual View (Source: [PCIe TDISP 1.0])

Figure 0-1 shows a conceptual view of TEE-IO component as an example.

This whitepaper's goal is to provide the guidance on how to build a device to meet the confidential computing requirement, as such the TVM can offload the workload to the device.

The organization of the white paper is as follows:

- Chapter 1 provides an overview on how the host software establishes the trust relationship with the device.

- Chapter 2 describes the software protocols and requirements for secure management of SPDM and IDE session management between TSM and DSM and for secure management of TDI assignment to a TVM.

- Chapter 3 describes the device and the host hardware shared responsibilities for ensuring access controls of data path MMIO and DMA access controls between a TDI and its corresponding TVM.

- Chapter 4 describes intra-device security requirements including isolation, integrity, and confidentiality protection of TDI and TVM private data, device identity, and measurement reporting and device firmware update.

- Appendix A specifies the specific requirements for TEE-IO device interoperability with the TDX Connect architecture.

# Glossary

| Term        | Description                              |

|-------------|------------------------------------------|

|             | Access Control Service                   |

| ACS         |                                          |

| ATS         | Address Translation Service              |

| СА          | Completer Abort                          |

| СМА         | Component Measurement and Authentication |

| CPL         | Completion                               |

| DOE         | Data Object Exchange                     |

| DSM         | Device Security Manager                  |

| EP Endpoint |                                          |

| FLR         | Function Level Reset                     |

| IDE         | Integrity and Data Encryption            |

| IDE_KM      | IDE Key Management                       |

| LN          | Lightweight Notification                 |

| LNR         | LN Request                               |

| MSI         | Message Signal Interrupt                 |

| NPR         | Non-Posted Request                       |

| P2P         | Peer to Peer                             |

| PASID       | Process Address Space ID                 |

| PR          | Posted Request                           |

| PRS         | Page Request Service                     |

#### Table 0-1: Glossary

| Term  | Description                            |

|-------|----------------------------------------|

| RP    | Root Port                              |

| SPDM  | Security Protocol and Data Model       |

| TDI   | TEE Device Interface                   |

| TDISP | TEE Device Interface Security Protocol |

| TEE   | Trusted Execution Environment          |

| TLP   | Transaction Layer Packet               |

| трн   | TLP Processing Hint                    |

| тѕм   | TEE Security Manager                   |

| тум   | TEE Virtual Machine                    |

| UC    | Unexpected Completion                  |

| UR    | Unsupported Request                    |

# 1 TEE-IO Device Architecture Overview

This chapter provides an overview of the TEE-IO device architecture.

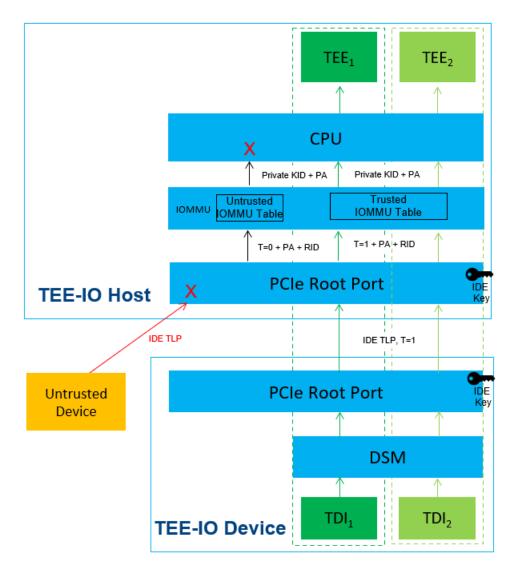

# **TEE-IO Security Model**

According to [PCIe TDISP 1.0], the TEE-I/O security model is primarily intended to apply to systems using device resources directly assigned to VMs. The device resource can be assigned as a TEE-IO Device Interface (TDI). The Before the TVM accepts a TDI, only the TSM and the host CPU are in the TEE TCB of the TVM. Once the TVM accepts a TDI, the TVM extends its TEE TCB to the entire TEE-IO device DSM, even if only one TDI from the device is accepted by the TVM.

The table 1-1 provides a summary of the shared security responsibility model of TDISP:

| Component | Role                     | Responsibilities                                |

|-----------|--------------------------|-------------------------------------------------|

| TSM       | TEE TCB for TVM, a       | Enforce security policies on the host.          |

|           | logic entity in a host.  |                                                 |

| DSM       | TEE TCB for TVM, a       | Enforce security policies on the device.        |

|           | logic entity in a device |                                                 |

| TVM       | TEE virtual machine on   | Admit the DSM into the TEE TCB. Accept the TDI. |

|           | host                     |                                                 |

| TDI       | Portion of the device    | Provide device functions to a TVM.              |

|           | assigned to a TVM        |                                                 |

| VMM       | Resource Manager         | Attach and detach TDIs to a TVM.                |

#### Table 1-1: Component in TEE-IO Security Model

Figure 1-1: Component in TEE-IO

# **Security Model for the Device**

According to [PCIe TDISP 1.0] (11.1 Overview of the TEE-I/O Security Model as it Relates to Devices, page 11), the security objective for a TEE-IO device is to protect the TVM data, code, and execution state with respect to:

- **Confidentiality**: protection from disclosure to entities such as firmware, software, or hardware not in the TEE TCB of the TVM (e.g., other TVMs, VMM, etc.).

- Integrity: protection from modification by entities such as firmware, software, or hardware not in the TEE TCB of the TVM (e.g., other TVMs, VMM, etc.). Replay-protection of the TVM data is also in scope.

There is no requirement for the protection of TVMs against denial-of-service attacks.

To achieve these security objectives, the device shall support:

- Device Identity Authentication and Measurement Reporting. In order to protect a TVM from TEE-IO device identity spoofing, the device shall implement a root-of-trust (ROT) for measurement (RTM), storage (RTS) and reporting (RTR) to support identity authentication and measurement reporting. The device debug interface shall not impact the device security properties. See Chapter 4 for detail.

- 2. Authenticated Secure Communication. The device shall use a secure communication channel to transfer the trusted data between the host and the device. The secure channel shall provide confidentiality, integrity, replay protection and message ordering protection. See Chapter 2 Secure Protocol and Data Model (SPDM) for management communication channel and Chapter 3 Integrity and Data Encryption (IDE) stream for data communication channel.

- 3. **TEE Device Interface (TDI) Management**. The device shall support locking down configurations of the TDI, reporting the configuration in a trusted manner, securely placing TDIs to operational state, and tearing them down securely when the TDI is detected. See Chapter 2 TEE Device Interface Security Protocol (TDISP) and Chapter 3 PCI Express Transaction Layer Packet (TLP) Rule for TDI.

- 4. **Device Security Architecture**. The device shall provide isolation and access control for the TVM data in the device for protection against the entities not in the trust boundary of TVM (such as the VMM, other TVMs, untrusted device component, other TDIs). The device should implement Advanced Error Reporting (AER) to report errors according to [PCIe TDISP 1.0] page 13. See Chapter 4 for detail.

# Implementing TEE-IO Device Stack

According to [PCIe TDISP 1.0] page 13, the device memory could be system level memory (defined as non-TEE memory), or TDI specific memory (defined as TEE memory). The TEE

#### TEE-IO Device Architecture Overview

memory shall have mechanisms to ensure the confidentiality and optional integrity of TVM data.

The device implementation to support TEE-IO can be separated as software stack and hardware stack. Usually, the **TEE-IO software stack** is to transfer the management information, such as device identity, device measurement, data encryption key, TDI lock, TDI report, TDI attachment, TDI detachment, etc.

The **TEE-IO hardware stack** provides link encryption to ensure the link's confidentiality and integrity, downstream access control logic to prevent non-trusted MMIO access to TEE memory, and upstream logic to ensure device DMA TEE data sent with encrypted IDE TLP.

# Secure Device Interface Lifecycle Example

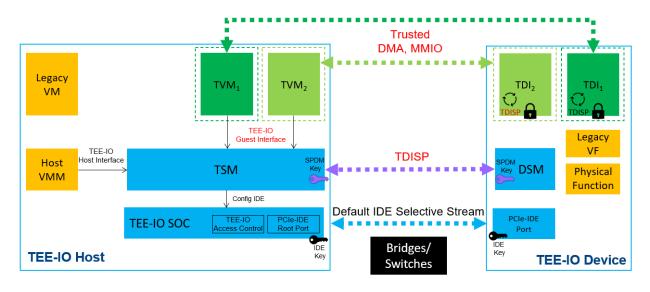

The following figures show the high-level software flow for TEE-IO architecture as a typical example.

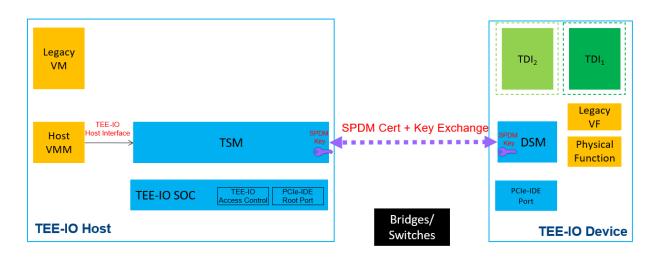

Step 1 (SPDM setup). See Figure 1-2. The VMM calls the TSM to establish the SPDM session with the device. Then the TSM will own the SPDM session. The TSM will also collect the device certificate and measurement and return to VMM for device attestation later. This step is per device.

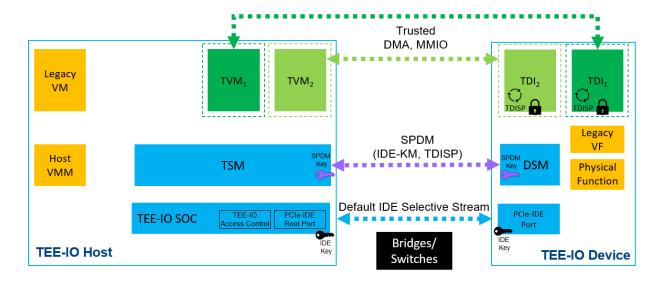

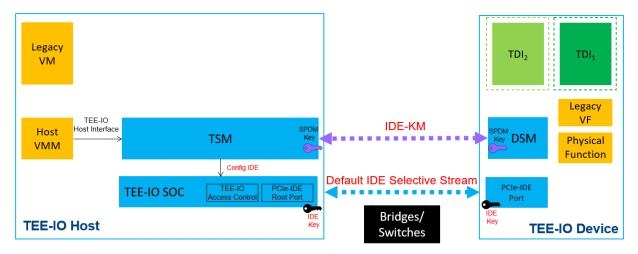

Step 2 (IDE Stream setup). See Figure 1-3. The VMM calls the TSM to use IDE\_KM to set up the default IDE selective steam with the device. The IDE\_KM is an SPDM vendor defined protocol sent in the SPDM session. The TSM will also configure the SOC IDE key programming register to ensure the IDE selective stream between SOC and device is established. After this step, the device and host SOC have two secure communication sessions. The SPDM session is a software session, which is used for software configuration such as IDE\_KM and TDISP. The IDE steam is hardware session, which is used to secure the PCI Express TLP. This step is also per device.

Step 3 (TDI assignment). See Figure 1-4. The VMM locks the TDI and launches a TVM, then assigns the TDI to the TVM.

- The TVM will get the device certificate and measurement from the TSM, then the TVM will verify the device based on a TVM specific policy. For example, the device certificate must have a trusted root Certificate Authority (CA) and the device measurement must match the latest reference manifest published by the device vendor. If the verification passes, the TVM can accept the TDI and use TDISP protocol to manage the TDI. If the verification fails, the TVM will reject the device.

- After the device is approved by the TVM, the VMM sets up the DMA and MMIO for the TDI and lets the TVM accept the configuration.

- Now TVM can start the TDI and use trusted DMA and MMIO to communicate with the TDI. This step is per device interface.

#### TEE-IO Device Architecture Overview

The VMM can repeat the same above process to assign another TDI to another TVM. See Figure 1-5. Note: One TVM may accept multiple TDIs. But one TDI must not be assigned to more than one TVM.

If a TDI is no longer needed, then the TVM or VMM can stop the TDI. If all TDIs in a device are removed, the VMM can remove the IDE stream and terminate the SPDM session for the device.

Appendix B provides more detail on SPDM management, IDE Stream management, and TDI lifecycle management.

Figure 1-2: Device SPDM Session Setup for Secure Communication

Figure 1-3: Device IDE Setup for Link Encryption

# intel.

Figure 1-4: TVM Launch and TDI Start

Figure 1-5: Another TVM Launch and TDI Start

# 2 TEE-IO Software Stack

This chapter describes the TEE-IO software stack requirement for the device. The device TEE-IO software stack implements the responder role of the secure device management protocols (i.e., SPDM, IDE\_KM and TDISP).

# **Software Stack Overview**

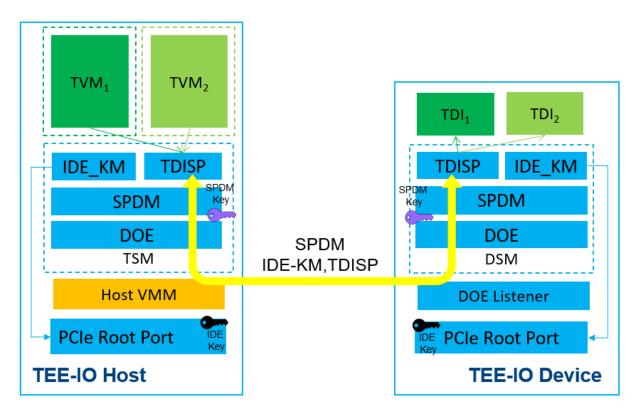

Figure 2-1 shows one example of implementing the TEE-IO software stack in the device.

The purpose of the TEE Device Interface Security Protocol (TDISP) protocol is to manage the TDI. The purpose of the Integrity and Data Encryption Key Management (IDE\_KM) protocol is to configure the IDE keys for the PCIe Root Port. Both IDE\_KM and TDISP are application-level protocols that are transported within a Secure Protocol and Data Model (SPDM) secure session for transport level protection. The SPDM messages are sent and received via PCI Data Object Exchange (DOE) interface.

#### Figure 2-1: Device DSM Software Stack

On the host side, the VMM manages the DOE mailbox to send or receive SPDM messages. The TSM acts as the security policy enforce to encrypt and decrypt SPDM secure messages, including IDE\_KM message and TDISP message. At runtime, the VMM or TVM requests the TSM to generate a protocol message request. Then the VMM sends the request to the device

DOE mailbox. Later, the VMM receives the response from the DOE mailbox and sends back to TSM to process it.

On the device side, there should be a listener to wait for SPDM messages. Then the SPDM stack in DSM will decrypt the SPDM secure messages and dispatch to TDISP or IDE\_KM callback to process the TDISP or IDE\_KM request message. Later, DSM will encrypt the TDISP or IDE\_KM response message and sends to DOE mailbox on the device.

# **Device Communication (DOE)**

PCI Express **Data Object Exchange (DOE)** ECN defines a mailbox mechanism for the host software to perform data object exchange with the device, such as a SPDM message or a secure SPDM message. The host uses the DOE to exchange messages with the device. One device may support multiple DOE mailboxes.

#### **Requirement:**

1. The device shall support SPDM over PCI DOE.

2. The device shall expose DOE Extended Capability registers for capability detection and control. [PCIe DOE 1.0] 7.9.xx Data Object Exchange (DOE) Extended Capability.

3. The device shall support the DOE 1.0 protocol including DOE Discovery (Data Object 0), CMA/SPDM (Data Object 1), Secure CMA/SPDM (Data Object 2). [PCIe DOE 1.0] 6.xx Data Object Exchange (DOE) and [PCIe IDE 1.0] 6.xx Data Object Exchange (DOE).

4. The device shall provide the DOE Extended Capability within function 0 to support the establishment of the SPDM session and transport secured messages. [PCIe TDISP 1.0] 11.2.2 TDISP message transport.

For TDX Connect compatibility, please refer to Appendix A "DOE" section.

# **Device Attestation (SPDM)**

The TVM needs to offload the confidential workload to the device TDI. As such, the TVM needs to verify the device.

PCI Express **Component Measurement and Authentication (CMA)** ECN defines the mechanism based upon Secure Protocol and Data Model (SPDM). The DSM provides the device certificate, authentication, and measurement reporting via SPDM.

#### **Requirement:**

1. The device shall support SPDM version 1.2.

2. The device shall support SPDM capability: CERT\_CAP and MEAS\_CAP, and support GET\_DIGEST, GET\_CERTIFICATE, and GET\_MEASUREMENTS.

3. The device shall support at least one of BaseAsymAlgo listed in CMA ECN: TPM\_ALG\_RSASSA\_3072, TPM\_ALG\_ECDSA\_ECC\_NIST\_P256, TPM\_ALG\_ECDSA\_ECC\_NIST\_P384.

4. The device shall support at least one of BaseHashAlgo listed in CMA ECN: TPM\_ALG\_SHA\_256, TPM\_ALG\_SHA\_384.

5. The device shall support at least one of MeasurementHashAlgo listed in CMA ECN: TPM\_ALG\_SHA\_256, TPM\_ALG\_SHA\_384.

6. The device shall support MeasurementSpecification: DMTF (bit 0).

7. The device certificate shall follow DSP0274 requirement. The X.509 certificate shall follow SPDM 1.2.1 Table 33 – Required fields. The X.509 certificate OID shall follow SPDM 1.2.1, 10.8.2, SPDM certificate requirements and recommendations, including 10.8.2.1 Extended Key Usage authentication OIDs, 10.8.2.2 SPDM Non-Critical Certificate Extension OID.

8. The device shall only return the DMTFSpecMeasurementValueType defined in SPDM 1.2.1. Table 45 – DMTF measurement specification format.

9. The DICE device shall support ALIAS\_CERT\_CAP and return DICE alias certificate.

10. The DICE alias certificate shall include DiceTcbInfo OID. The DiceTcbInfo shall include the firmware information such as digest and/or secure version number (SVN).

For TDX Connect compatibility, please refer to Appendix A "SPDM" section.

# Software Secure Communication (SPDM)

The TSM needs to establish an authenticated secure session with the device for integrity and confidentiality. This software secure session is used to exchange the hardware encryption key such as IDE\_KM protocol, or TDI management such as TDISP protocol.

DMTF **Secure Protocol and Data Model (SPDM)** provides an authenticated secure session between the host TSM and the device DSM. PCI Express Integrity and Data Encryption (IDE) ECN and TEE Device Interface Security Protocol (TDISP) ECN rely on SPDM for the secure management data communication.

### **Requirement:**

1. The device shall support SPDM capability: ENCRYPT\_CAP, MAC\_CAP, and KEY\_EX\_CAP, and support KEY\_EXCHANGE, FINISH, and END\_SESSION.

2. The device shall support at least one of DHE Group: secp256r1, secp384r1.

3. The device shall support at least one of AEAD Cipher Suite: AES-256-GCM.

4. The device shall support Key Schedule Algorithm: DMTF.

5. The device shall support DSP0274 OtherParamsSupport.OpaqueDataFmt1.

6. The device shall use DSP0277 version 1.1 as Secured Message transport binding version in the Secure Message opaque data.

7. The device should support KEY\_UPD\_CAP. If the device supports KEY\_UPD\_CAP, the device shall support update keys for both directions with UpdateAllKeys.

8. The device may support HBEAT\_CAP. If it is supported, the device session shall be terminated after twice HeartbeatPeriod.

9. The DSM shall teardown the session if a firmware update is triggered, if the SPDM 1.2 SessionPolicy.TerminationPolicy = 0.

10. The DSM shall keep the confidentiality of the SPDM session key.

11. The DSM may perform mutual authentication based upon the TSM capability during SPDM session establishment, or DSM may perform TVM authentication in an established SPDM session. This is use case specific.

**NOTE:** The TSM may be implemented in software, making it hard to provision a public certificate and a private key to sign the SPDM message at session creation. The TSM may use a non-standardized TEE-Quote based certificate as described in Remote-Attestation TLS (RA-TLS) to support quote-based mutual attestation. Or the TSM/DSM may use two-phase authentications: In phase 1 TSM attests the device as described in SPDM specification; in phase 2 DSM authenticates the host environment including host TEE TCB (CPU and TSM), host TVM, and so on with an implementation specific mechanism.

For TDX Connect compatibility, please refer to Appendix A "SPDM" section.

# Link Encryption Key Management (IDE\_KM)

The TSM needs to setup link encryption with the device to mitigate possible attacks in the path between the host and device.

PCI Express **Integrity and Data Encryption (IDE)** ECN provides confidentiality, integrity, and replay protection for Transaction Layer Packet (TLP) transmitted and received between two PCI Express ports. The TSM uses IDE key management (IDE\_KM) protocol to manage the IDE keys with the DSM, such as programming the IDE key, starting or stopping the IDE stream. The

DSM configures the IDE encryption keys in the device. Please refer to Chapter 3, IDE Stream section, for an example on how to setup IDE stream, stop IDE stream, etc.

#### **Requirement:**

1. The DSM shall support IDE\_KM payload in SPDM vendor defined message. [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 19.

2. The device shall expose DOE for IDE in Function 0. [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 20.

3. The DSM shall support IDE\_KM messages QUERY. [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 21.

4. The DSM shall support IDE\_KM messages KEY\_PROG. [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 22.

5. The DSM shall support IDE\_KM messages SET\_K\_GO. [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 23.

6. The DSM shall support IDE\_KM messages SET\_K\_STOP. [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 24.

7. The DSM shall handle IDE enable/disable in IDE Stream Enable bit, according to [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 24.

8. The DSM shall manage the Secure/Insecure State correctly in SPDM secure session, according to [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 24.

9. The DSM shall handle key correctly, according to [PCIe IDE 1.0] 6.99.3 IDE Key Management (IDE\_KM), page 26. The key set bit shall be used for the key update.

For TDX Connect compatibility, please refer to Appendix A "IDE\_KM" section.

# **Device Interface Management (TDISP)**

One device may be used by multiple TVMs. The VMM needs to assign the TDI in the device to the TVM. Also, the TVM needs to decide to start or stop the TDI.

PCI Express **TEE Device Interface Security Protocol (TDISP)** ECN defines such mechanism. The TVM and VMM may use TDISP protocol to manage the device TDI. The DSM provides the interface management, such as TDI configuration lock with policy (such as NO\_FW\_UPDATE) and reporting, and TDI attach and detach.

#### **Requirement:**

1. The DSM shall ensure the IDE\_KM (for IDE keys establishment) and TDISP (for TDI management) using same SPDM session. [PCIe TDISP 1.0] 11.1 Overview of the TEE-I/O Security Model as it Relates to Devices, page 15.

2. If implemented, the DSM shall follow the peer-to-peer (P2P) communication rule to set up P2P stream, according to [PCIe TDISP 1.0] 11.2 TDISP Rules, page 19.

3. The DSM shall support TDISP payload in SPDM vendor defined message, according to [PCIe TDISP 1.0] 11.2.2 TDISP Message Transport, page 21.

4. The DSM shall follow Requirements for Responders (DSM), according to [PCIe TDISP 1.0] 11.2.4 Requirements for Responders (DSM), page 22.

5. The DSM shall follow DSM Tracking and Handling of Locked TDI Configurations, according to [PCIe TDISP 1.0] 11.2.6 DSM Tracking and Handling of Locked TDI Configurations, page 23.

6. The DSM shall support TDISP required messages: TDISP\_VERSION, TDISP\_CAPABILITIES, LOCK\_INTERFACE\_RESPONSE, DEVICE\_INTERFACE\_REPORT, DEVICE\_INTERFACE\_STATE, START\_INTERFACE\_RESPONSE, STOP\_INTERFACE\_RESPONSE.

7. The DSM shall follow TDISP Message Format and Protocol Versioning, according to [PCIe TDISP 1.0] 11.3.3 TDISP Message Format and Protocol Versioning, page 28.

8. The DSM shall support GET\_TDISP\_VERSION according to [PCIe TDISP 1.0] 11.3.4 GET\_TDISP\_VERSION, page 30 and 11.3.5 TDISP\_VERSION, page 30.

9. The DSM shall support GET\_TDISP\_CAPABILITIES according to [PCIe TDISP 1.0] 11.3.6 GET\_TDISP\_CAPABILITIES, page 30 and 11.3.7 TDISP\_CAPABILITIES, page 31.

The DSM shall support a DEV\_ADDR\_WIDTH that is equal to or larger than host address width, to prevent address alias attack.

10. The DSM shall support LOCK\_INTERFACE\_REQUEST according to [PCIe TDISP 1.0] 11.3.8 LOCK\_INTERFACE\_REQUEST, page 31 and 11.3.9 LOCK\_INTERFACE\_RESPONSE, page 34.

11. The DSM shall support GET\_DEVICE\_INTERFACE\_REPORT according to [PCIe TDISP 1.0] 11.3.10 GET\_DEVICE\_INTERFACE\_REPORT, page 35 and 11.3.11 DEVICE\_INTERFACE\_REPORT, page 36. The DSM shall generate the TDI report according to [PCIe TDISP 1.0] Table 15 TDI Report Structure, page 37.

12. The DSM shall support GET\_DEVICE\_INTERFACE\_STATE according to [PCIe TDISP 1.0] 11.3.12 GET\_DEVICE\_INTERFACE\_STATE, page 40 and 11.3.13 DEVICE\_INTERFACE\_STATE, page 40.

13. The DSM shall support START\_INTERFACE\_REQUEST according to [PCIe TDISP 1.0] 11.3.14 LOCK\_INTERFACE\_REQUEST, page 40 and 11.3.15 START\_INTERFACE\_RESPONSE, page 41.

14. The DSM shall support STOP\_INTERFACE\_REQUEST according to [PCIe TDISP 1.0] 11.3.16 LOCK\_INTERFACE\_REQUEST, page 41 and 11.3.17 STOP\_INTERFACE\_RESPONSE, page 42.

15. If implemented, the DSM shall support BIND\_P2P\_STREAM\_REQUEST according to [PCIe TDISP 1.0] 11.3.18 BIND\_P2P\_STREAM\_REQUEST, page 42 and 11.3.19 BIND\_P2P\_STREAM\_RESPONSE, page 43.

16. If implemented, the DSM shall support UNBIND\_P2P\_STREAM\_REQUEST according to [PCIe TDISP 1.0] 11.3.20 UNBIND\_P2P\_STREAM\_REQUEST, page 43 and 11.3.21 UNBIND\_P2P\_STREAM\_RESPONSE, page 44.

17. If implemented, the DSM shall support SET\_MMIO\_ATTRIBUTE\_REQUEST according to [PCIe TDISP 1.0] 11.3.22 SET\_MMIO\_ATTRIBUTE\_REQUEST, page 44 and 11.3.23 SET\_MMIO\_ATTRIBUTE\_RESPONSE, page 45.

18. The DSM shall support TDISP\_ERROR according to [PCIe TDISP 1.0] 11.3.24 TDISP\_ERROR, page 46.

19. If implemented, the DSM shall support VDM\_REQUEST according to [PCIe TDISP 1.0] 11.3.25 VDM\_REQUEST, page 48 and 11.3.26 VDM\_RESPONSE, page 48.

For TDX Connect compatibility, please refer to Appendix A "TDISP" section.

# **Implementation Reference**

## SPDM software stack

The DMTF open sourced SPDM sample implementation at <u>https://github.com/DMTF/libspdm</u>.

| Component                             | Purpose                                                                                                             | URL                                                                                     |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| spdm_resp<br>onder_lib                | Responder library. It can be used on the device side.                                                               | https://github.com/DMTF/libspdm/tree/<br>main/library/spdm_responder_lib                |

| spdm_requ<br>ester_lib                | Requester library. It can be used to test the device.                                                               | https://github.com/DMTF/libspdm/tree/<br>main/library/spdm_requester_lib                |

| spdm_devic<br>e_secret_lib<br>_sample | sample device library to support<br>measurement reporting and digital<br>signature generation on the device<br>side | https://github.com/DMTF/libspdm/tree/<br>main/os_stub/spdm_device_secret_lib_<br>sample |

#### Table 2-1: SPDM software Stack Reference

| spdm-emu                         | An SPDM requester emulator,<br>which may be used to test the<br>device SPDM stack. | https://github.com/DMTF/spdm-emu                     |

|----------------------------------|------------------------------------------------------------------------------------|------------------------------------------------------|

| spdm-<br>dump                    | A tool to dump SPDM messages with PCAP format.                                     | https://github.com/DMTF/spdm-dump                    |

| SPDM-<br>Responder-<br>Validator | A test suite for the SPDM device                                                   | https://github.com/DMTF/SPDM-<br>Responder-Validator |

## IDE\_KM software stack

The DMTF open sourced SPDM sample implementation includes an IDE\_KM software example.

| Component                            | Purpose                                               | URL                                                                                                      |

|--------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| pci_ide_km<br>_responder<br>_lib     | Responder library. It can be used on the device side. | https://github.com/DMTF/spdm-<br>emu/tree/main/library/pci_ide_km_resp<br>onder_lib                      |

| pci_ide_km<br>_requester_<br>lib     | Requester library. It can be used to test the device. | <u>https://github.com/DMTF/spdm-</u><br><u>emu/tree/main/library/pci_ide_km_requ</u><br><u>ester_lib</u> |

| pci_ide_km<br>_device_lib<br>_sample | sample device library to support IDE_KM messages.     | https://github.com/DMTF/spdm-<br>emu/tree/main/library/pci_ide_km_devi<br>ce_lib_sample                  |

#### Table 2-2: IDE\_KM software Stack Reference

## **TDISP** software stack

The DMTF open sourced SPDM sample implementation includes a TDISP software example.

#### Table 2-3: TDISP software Stack Reference

| Component    | Purpose                              | URL                                              |

|--------------|--------------------------------------|--------------------------------------------------|

| pci_tdisp_re | Responder library. It can be used    | https://github.com/DMTF/spdm-                    |

| sponder_lib  | on the device side.                  | emu/tree/main/library/pci_tdisp_reques           |

|              |                                      | ter_lib                                          |

| pci_tdisp_re | Requester library. It can be used to | https://github.com/DMTF/spdm-                    |

| quester_lib  | test the device.                     | <pre>emu/tree/main/library/pci_tdisp_respo</pre> |

|              |                                      | nder_lib                                         |

# intel

| pci_tdisp_d  | sample device library to support | https://github.com/DMTF/spdm-                     |

|--------------|----------------------------------|---------------------------------------------------|

| evice_lib_sa | IDE_KM messages.                 | <pre>emu/tree/main/library/pci_tdisp_device</pre> |

| mple         |                                  | <u>_lib_sample</u>                                |

# 3 TEE-IO Hardware Stack

This chapter describes the TEE-IO hardware stack requirement on the device side. The TEE-IO hardware stack is the data encryption engineer to support trusted MMIO and trusted DMA, and hardware registers such as data encryption key, TDI state, etc.

# **IDE Stream**

IDE secures the TLP traffic from one port to another port. IDE TLP Prefix includes a "**T bit**", which indicates the TLP originated from within a trusted execution environment. The "T bit" provides a mechanism to distinguish TLPs that are associated with a TVM. IDE mechanisms ensure that the T bit (like other TLP content) is secured during transit.

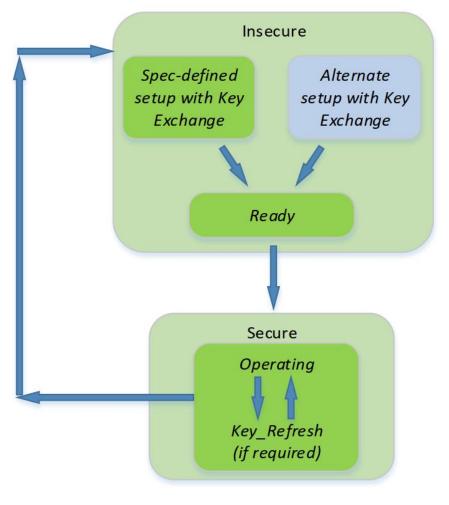

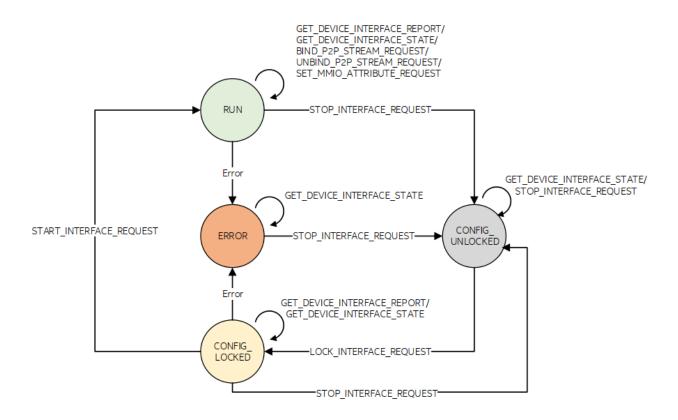

IDE Stream State Machine includes Insecure or Secure state. See figure 3-1.

*Secure State*: The device IDE Stream shall enter Secure State only after all necessary steps are done, including the keys are programmed, and the IDE stream is enabled.

*Insecure State*: The device IDE Stream shall enter an Insecure state if any necessary steps are not met. For example, the IDE stream is disabled, or IDE Check Failed error happens.

**Ready sub-state**: This is a sub-state of Insecure state. The device has all keys programmed. The only rest step is to trigger IDE stream. The trigger action requires both K\_SET\_GO messages and IDE Stream Enable bit set in the IDE Extended Capability Register.

# intel.

Figure 3-1: IDE Stream State Machine (Source: [PCIe IDE 1.0])

#### **Requirement:**

1. The device shall maintain the IDE Stream Secure State and Insecure State, according to [PCIe IDE 1.0] 6.99.1 IDE Stream and TEE State Machines, page 16.

2. The device shall implement IDE Extended Capability in function 0. [PCIe IDE 1.0] 6.99.2 IDE Stream Establishment, page 18.

3. The device shall follow IDE TLP rule, according to [PCIe IDE 1.0] 6.99.4 IDE TLPs, page 29. The device shall use IDE TLP Prefix for all IDE TLPs.

4. The device shall follow a selective IDE stream rule, according to [PCIe IDE 1.0] 6.99.4 IDE TLPs, page 33. The device shall follow "Table XX – TLP Types for Selective IDE Streams" to only permit MRd, MRdLk, MWr, CfgRd1, CfgWr1, DMWr, Msg\*, MsgD\*, Cpl, CplD, CplLk, CplDLk, FetchAdd, Swap, and CAS. The IORd, IOWr, CfgRd0, and CfgWr0 are not encrypted.

5. The device shall follow IDE TLP sub-stream rule, according to [PCIe IDE 1.0] 6.99.5 IDE TLP Sub-streams, page 38.

6. The device shall follow IDE TLP Aggregation, if it is supported, according to [PCIe IDE 1.0] 6.99.6 IDE TLP Aggregation, page 40.

7. The device shall follow other IDE Rules for Non-Posted IDE Requests, according to [PCIe IDE 1.0] 6.99.8 Other IDE Rules, page 44.

8. The device shall follow other IDE Rules for resets, according to [PCIe IDE 1.0] 6.99.8 Other IDE Rules, page 44. Conventional Reset or Function Level Reset (FLR) to a function with IDE shall change to Insecure state. FLR to a function without IDE shall not affect IDE operation.

9. The device shall follow other IDE Rules for Access Control Services (ACS), according to [PCIe IDE 1.0] 6.99.8 Other IDE Rules, page 44.

10. The device shall follow other IDE Rules for error handling, according to [PCIe IDE 1.0] 6.99.8 Other IDE Rules, page 45. Detecting IDE Check Failed error, MAC check failure, underflow or overflow of TLP counter shall change to Insecure State.

11. The device shall follow other IDE Rules for power management, according to [PCIe IDE 1.0] 6.99.8 Other IDE Rules, page 46. No\_Soft\_Reset bit shall be Set. All state related to keys and counters shall be maintained in D0, D1, D2, and D3hot. They may be maintained in D3cold.

12. The device shall follow other IDE Rules for secure local environment, according to [PCIe IDE 1.0] 6.99.8 Other IDE Rules, page 46. Attempts to modify IDE registers, BARs, and other structures that could affect the security or an IDE Stream shall be detected and enter Insecure state.

13. The device shall implement IDE Extended Capability, according to [PCIe IDE 1.0] 7.9.99 IDE Extended Capability, page 48.

14. The device shall expose "TEE-IO Supported" in Device Capability Register. [PCIe TDISP 1.0] 6.33.4 IDE TLPs, page 5.

15. The device shall implement bit 7 of Sub-Stream field as Reserved. [PCIe TDISP 1.0] 6.33.4 IDE TLPs, page 5.

16. The device shall follow rule when TEE-IO Supported is set, according to [PCIe TDISP 1.0] 6.33.4 IDE TLPs, page 6.

17. The device shall follow rule for Non-Posted IDE Requests based upon TEE-IO Supported bit, according to [PCIe TDISP 1.0] 6.33.8 Other IDE Rules, page 7.

### **IDE Stream Precedence**

The device shall follow IDE stream precedence rule, according to [PCIe IDE 1.0] 6.99.4 IDE TLPs, page 37. The rule is summarized as follows:

#### a. For transmitter:

```

if (IAAR and IRAR rule hit) {

Stream ID := corresponding Stream ID

} else if (default Selective IDE Stream is configured) {

Stream ID := default Selective IDE Stream ID

} else if (Link IDE Stream is enabled) {

Stream ID := Link IDE Stream ID

} else {

Stream ID := invalid // Not use IDE-TLP

}

```

Where IAAR == IDE Address Association Register, IRAR = IDE RID Association Register.

#### b. For receiver:

Stream ID := Stream ID in the received IDE TLP Prefix

#### **TEE Limited Stream**

TEE limited stream is optional. It indicates that only those TLPs that have the T bit Set are permitted to be **associated with** this Stream. This is for optimization purpose, because not all data in TVM requires the protection.

**Note:** This IDE features requires same capability to be supported and configured on the host Root Port to function correctly. For more details, please refer to [PCIe IDE 1.0].

#### **Requirement if implemented:**

1. If implemented, the device shall follow the description for TEE Limited Stream, according to [PCIe TDISP 1.0] 7.9.26.5.2: Selective IDE Stream Control Register, page 8.

#### **Partial Header Encryption**

Partial header encryption is added in [PCIe 6.0] as an optional feature. It provides the ability to reduce potential exposure to side-channel attacks by encryption some portions of the Header

of an IDE Memory Request while maintaining information that is required for TLP routing and low-level TLP processing in the clear.

**Note:** This IDE features requires same capability to be supported and configured on the host Root Port to function correctly. For more details, please refer to [PCIe IDE 1.0].

#### **Requirement if implemented:**

1. If implemented, the device shall follow the description for partial header encryption, according to [PCIe 6.0] 7.9.26.2 IDE Capability Register, 7.9.26.4.1 Link IDE Stream Control Register, 7.9.26.5.2 Selective IDE Stream Control Register.

For TDX Connect compatibility, please refer to Appendix A "IDE Stream" section.

# **TDI TLP Rule**

The device function unit may have:

- **TDI**: A Trusted Device Interface. It may be an entire device, a physical function (PF) or virtual function (VF). It may be in CONFIG\_UNLOCK, CONFIG\_LOCK, RUN, or ERROR state. A TDI shall be isolated from non-TDI and other TDIs by the DSM.

- **Non-TDI**: A legacy device function unit, which cannot be assigned as a TDI by definition. It may be a physical function (PF) or virtual function (VF).

- **DSM**: A device security manager, which is the TEE TCB for all TDIs.

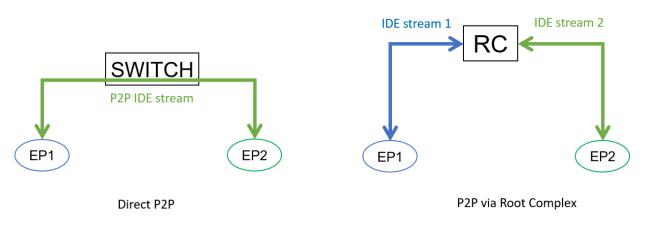

A TDI state machine includes 4 states (see Figure 3-2):

**CONFIG\_UNLOCKED**: This is the initial, default state of a TDI. There is no security property (confidentiality and optional integrity) that a TDI needs to provide to the TVM data. The DSM shall not allow interface start.

**CONFIG\_LOCKED**: This is the intermediate transition state from default to RUN. To enter this state, the VMM should finish configuration, and TSM should explicitly send LOCK\_INTERFACE. The DSM or TDI is expected to clean up and prepare to provide the security property. For example, all previous MMIO requests or DMA requests should be dropped.

*RUN*: This is the actual functional state. TVM can send START\_INTERFACE to explicitly request the TDI to enter this state. The TDI can perform trusted MMIO or DMA transaction to communicate with TVM.

**ERROR**: This is the error state. When the DSM or TDI detects any change impacting device configuration or security in CONFIG\_LOCKED or RUN state, the TDI shall be changed to ERROR state. TDI shall not expose any confidential TVM data. TDI may start cleaning up the TVM data.

Figure 3-2: TDI State Machine (Source: [PCIe TDISP 1.0])

The host function unit may have

- **TEE VM (TVM)**: A VM requiring the TEE capability. A TVM shall be isolated from VMM, legacy VM, and other TVM by the TSM.

- Legacy VM: A VM not requiring the TEE capability.

- VMM: A system resource manager for TVM and Legacy VM.

- **TSM**: A TEE security manager, which is TCB for all TVMs.

The connection between the device and the host:

- **TVM <-> TDI**: Follow TLP rules for MMIO, DMA, ATS, etc.

- Legacy VM <-> TDI: Not the focus of the TDISP specification. \*

- Legacy VM/VMM <-> Non-TDI: Legacy behavior. Out of scope.

- **TSM <-> DSM**: Follow SPDM, IDE\_KM, TDISP protocol.

\* NOTE: For Legacy VM <-> TDI, it is permitted for IDE streams established by the TSM to be used to carry TLPs associated with legacy VMs. [PCIe TDISP 1.0] 11.1 page 14. For a TDI that supports assignment to Legacy VMs, if a TDI is assigned to a Legacy VM, the VMM assigns the TDI in CONFIG\_UNLOCKED, and the TSM must ensure that the TDI remains in that state unless and until the TDI is removed from the Legacy VM and prepared for re-assignment to a TDI. [PCIe TDISP 1.0] 11.1 page 18.

According to [PCIe TDISP 1.0], a device implementation may support legacy VM <> TDI. If a TDI is assigned to a legacy VM, the TDI is allowed to transmit or receive messages (such as MMIO or DMA) in Non-IDE Stream in CONFIG\_UNLOCK state. Once the TDI is asked to transit to CONFIG\_LOCK state, the TDI should drain all pending requests and received data in CONFIG\_UNLOCK state.

In order to facilitate the TLP rule discussion, we define the following terms:

- Bound IDE stream: The IDE stream bound to a TDI. In normal case, it is the default stream in LOCK\_INTERFACE\_REQUEST [PCIe TDISP 1.0] 11.3.8. The IDE specification defined "default stream" in [PCIe IDE 1.0] 7.9.99.5.2 Selective IDE Stream Control Register. If a device includes multiple TDIs, those TDIs may share the same default stream. In direct peer to peer (P2P) case, the Bound IDE stream is the P2P stream in BIND\_P2P\_STREAM\_REQUEST [PCIe TDISP 1.0] 11.3.18.

- Non-Bound IDE Stream: The IDE stream not bound to this TDI.

- Non-IDE Stream: The plaintext TLP (not encrypted).

- **TEE-TLP**: TLP Bound IDE stream with T=1.

- Non-TEE-TLP: All the other not TEE-TLP, such as TLP Bound IDE stream with T=0, Non-Bound IDE Stream with T=0 or T=1, or Non-IDE Stream.

NOTE: The "T bit" indicates that the TLP originated **from** within a trusted execution environment (TEE). However, there is no bit to indicate if **the target** is within TEE or non-TEE. This is a known limitation so far. As such, the device should not use a common shared cache to store the data, unless the device cache has an attribute to identify if the cache-entry is private (TEE) or shared (non-TEE).

NOTE: the following rules are only for TDI, but not for non-TDI.

### **TDI as Completer**

Resource definition:

- TEE MMIO (T-MMIO): The TEE memory in the device, read/write from the host, which must have mechanisms to ensure the confidentiality of TVM data, and optionally integrity. [PCIe TDISP 1.0] 11.1. page 13. It is NON\_TEE\_MEM=0 in the TDI report structure. TEE MMIO is only present when TDI is in CONFIG\_LOCK, RUN, or ERROR state. TEE MMIO does not exist when TDI is in CONFIG\_UNLOCK state.

- Non-TEE MMIO (NT-MMIO): The Non-TEE memory in the device, read/write from the host, which does not have above protection mechanism. It is NON\_TEE\_MEM=1 in the TDI report structure.

- **CFG**: The device configuration space read/write from the host. It is not required that Configuration Requests to a TDI be secured. [PCIe TDISP 1.0] 11.2. page 20.

Rule definition:

• Success (V): The device shall process and return success completion (SC) TLP for NPR.

• **Reject (X)**: The device shall return an Unsupported Request (UR) TLP or drop the received TLP.

#### NOTE:

1. "If the result is a determination that the TLP must be rejected, the associated TDI must transition to ERROR where indicated, but no further error reporting or logging is required to be performed on that TLP," [PCIe TDISP 1.0] 11.2. TDISP Rules Page 18. Here the "rejected" means the "IDE Check Failed" instead of access control rule. "no further error reporting is required" because there is no trusted way to guarantee that the device error message is delivered to the TVM. The man-in-the-middle adversary can block or delay the error reporting regardless of whether it is a hardware mechanism or a software mechanism. Please refer to Chapter 4, Error Handling Section.

2. "If the result is a determination that the **TLP must be rejected**, ... it is optionally permitted on a **case-by-case** basis to handle a Request as an **Unsupported Request**, and/or handle a Completion as an **Unexpected Completion**, or that the TLP be **dropped**." [PCIe TDISP 1.0] 11.2. TDISP Rules Page 18. In the case of rejection, the TLP can be responded with UR/UC or dropped.

Table 3-4, Table 3-5 and Table 3-6 are the rule summary of TDI acting as a Completer, according to [PCIe TDISP 1.0] 11.2.1 TLP Rules, page 21.

| Access Control | CONFIG_UNLOCK | CONFIG_LOCK | RUN        | ERROR      |

|----------------|---------------|-------------|------------|------------|

| TEE-TLP        | N/A *         | T-MMIO (X)  | T-MMIO (V) | T-MMIO (X) |

| Non-TEE-TLP    | N/A **        | T-MMIO (X)  | T-MMIO (X) | T-MMIO (X) |

#### Table 3-4: TEE-MMIO Rule Summary for TDI as Completer

\* By definition, the Bound IDE stream is only known after LOCK\_INTERFACE\_REQUEST is sent. As such, there is no TEE-TLP in CONFIG\_UNLOCK. All TLPs in CONFIG\_UNLOCK are non-TEE-TLP.

\*\* By definition, the TDI does not provide confidentiality or optional integrity of the TVM data in CONFIG\_UNLOCK, if the TDI is assigned to a legacy VM. As such, the TDI does not have any TEE-MMIO, because a TDI is not required to protect confidential data placed into it in this state.

#### Table 3-5: NON-TEE-MMIO Rule Summary for TDI as Completer

| Access Control | CONFIG_UNLOCK | CONFIG_LOCK | RUN         | ERROR       |

|----------------|---------------|-------------|-------------|-------------|

| TEE-TLP        | N/A           | NT-MMIO (V) | NT-MMIO (V) | NT-MMIO (V) |

| Non-TEE-TLP    | NT-MMIO (V)   | NT-MMIO (V) | NT-MMIO (V) | NT-MMIO (V) |

Table 3-6: CFG Rule Summary for TDI as Completer

| Access Control | CONFIG_UNLOCK | CONFIG_LOCK | RUN     | ERROR   |

|----------------|---------------|-------------|---------|---------|

| TEE-TLP        | N/A           | CFG (V)     | CFG (V) | CFG (V) |

| Non-TEE-TLP    | CFG (V)       | CFG (V)     | CFG (V) | CFG (V) |

NOTE:

1. **TEE MMIO**: TEE MMIO is only allowed with bound IDE stream, T=1, and TDI in RUN.

```

if ((TDI.STATE != RUN) ||

(TLP.T == 0) ||

(STREAM_TYPE != IDE_TLP) ||

(IDE_STREAM_ID != TDISP_BOUND_STREAM_ID) ||

(TLP.ADDRESS NOT IN STREAM-ASSOCIATION-RANGES[N])) {

Access = Deny;

} else {

Access = Allow;

}

```

2. **Non-TEE MMIO**: [PCIe TDISP 1.0] mentioned the rule for TDI acting as a Completer: "Requests targeting device memory received with the T bit Set while in any state other than RUN must be rejected.". That rule is superseded by "The TDI's handling is not modified by TDISP state for Received Memory Requests targeting MMIO with IS\_NON\_TEE\_MEM Set."

3. **CPL** rule: The value of the T bit in the Completion(s) returned by the TDI **must match** the value of the T bit in the corresponding Request. [PCIe TDISP 1.0].

4. **CFG** rule: It is not required that Configuration Requests to a TDI be secured. [PCIe TDISP 1.0] 11.2. page 20. [PCIe IDE 1.0] Table XX–TLP Types for Selective IDE Streams mentions Type0 is not permitted for selective IDE streams, because we do not expect that will happen. A proper requester shall always use Type1. An improper requester may use Type0. The device may choose to accept or reject, but it does not impact security.

## **TDI as Requester**

Resource definition:

• **DMA**: The host memory-read/write from the device. The device does not know if the host memory is TEE memory or non-TEE memory, according to [PCIe TDISP 1.0].

- **MSI**: The message signaled interrupt from the device to the host.

- **Trusted-MSI (T-MSI)**: The LOCK\_MSIX flag in LOCK\_INTERFACE\_REQUEST is 1 and MSIX table is part of locked MMIO\_RANGE.

Rule definition:

- Allowed (V): The device can send the TLP.

- Not allowed (X): The device shall not send the TLP. It is DSM/TDI's responsibility.

Table 3-7, Table 3-8, and Table 3-9 are rule summary of TDI acting as a Requester, according to [PCIe TDISP 1.0] 11.2.1 TLP Rules, page 20.

#### Table 3-7: DMA Rule Summary for TDI as Requester

| Operation   | CONFIG_UNLOCK | CONFIG_LOCK | RUN     | ERROR   |

|-------------|---------------|-------------|---------|---------|

| TEE-TLP     | N/A           | DMA (X)     | DMA (V) | DMA (X) |

| Non-TEE-TLP | DMA (V) **    | DMA (X)     | DMA (X) | DMA (X) |

\*\* DMA is allowed in CONFIG\_UNLOCK, if the TDI is designed to a Legacy VM.

#### Table 3-8: MSI Rule Summary for TDI as Requester

| Operation   | CONFIG_UNLOCK | CONFIG_LOCK | RUN     | ERROR   |

|-------------|---------------|-------------|---------|---------|

| TEE-TLP     | N/A           | MSI (X)     | MSI (X) | MSI (X) |

| Non-TEE-TLP | MSI (V)       | MSI (V)     | MSI (V) | MSI (V) |

#### Table 3-9: Trusted-MSI Rule Summary for TDI as Requester

| Operation   | CONFIG_UNLOCK | CONFIG_LOCK | RUN       | ERROR     |

|-------------|---------------|-------------|-----------|-----------|

| TEE-TLP     | N/A           | T-MSI (X)   | T-MSI (V) | T-MSI (X) |

| Non-TEE-TLP | N/A **        | T-MSI (X)   | T-MSI (X) | T-MSI (X) |

\*\* Trusted-MSI is not applicable, only non-trusted MSI is allowed.

NOTE:

1. **DMA** rule: DMA is only allowed with bound IDE stream, T=1, and when TDI in RUN.

```

if (TDI.STATE != RUN) {

Operation = Deny;

} else {

Operation = Allow;

TLP.T = 1;

```

}

```

STREAM_TYPE = IDE_TLP;

IDE_STREAM_ID = TDISP_BOUND_STREAM_ID;

```

2. **CPL** rule: For Memory Reads issued by the TDI while in RUN, the corresponding Completion(s) must be handled normally if and only if the TDI is still in RUN and must otherwise be rejected. [PCIe TDISP 1.0]. "Still in RUN" means that the TDI shall not change to ERROR state then back to RUN state again.

A TDI in RUN **must ignore** the value of the T bit in Received Completions. [PCIe TDISP 1.0]. The reason is that the host SOC implementation may set T=0 for non-TEE owned shared memory.

Receipt of a Completion with UR/CA or Completion timeout (following recovery retries) for request initiated by a TDI in CONFIG\_LOCK, RUN (with T=1) indicates occurrence of an uncorrectable error, TDI must transition to ERROR. [PCIe TDISP 1.0] 11.4.3. Securing Interconnects.

3. **MSI** rules: The T-bit must be set according to LOCK\_MSIX flag in LOCK\_INTERFACE\_REQUEST and MSIX table is part of locked MMIO\_RANGE, if TDI is in RUN state.

```

if ((TDI.STATE == RUN) &&

(LOCK_MSIX flag == 1) &&

(MSIX table is part of locked MMIO_RANGE)) {

TLP.T = 1;

} else {

TLP.T = 0;

}

```

An MSI with T-bit clear is always allowed in CONFIG\_UNLOCK or ERROR state, although it is not explicit stated in TDISP specification, because there is no security property required.

# **ATS Rule**

The presence of DMA address translation in the host system has certain performance implications for DMA accesses. To mitigate these impacts, a device may include an address translation cache (ATC), which is also known as device translation look-aside buffer (Device TLB). Address translation service (ATS) uses a request-completion protocol between a Device and a Root Complex (RC) to provide translation services. In addition, a new Address Type (AT) field is defined within the Memory Read and Memory Write TLP. The new AT field could be Untranslated, Translation Request, Translated.

# intel

## **3** TEE-IO Hardware Stack

ATS improves the behavior of DMA based data movement. An associated Page Request service (PRS) provides additional advantages by allowing DMA operations to be initiated without requiring that all the data to be moved into or out of system memory be pinned. Allowing a device to operate more independently (to page fault when it requires memory resources that are not present) provides a superior level of coupling between device and host.

ATS TLP Type definition:

- Translated read/write: Follow the same rule as Memory read/write for DMA/MMIO.

- **Translation Request (TRANS)**: The translation request from the device Address Translation Cache (ATC) to the host Translation Agent (TA).

- **Translation Completion (TRANS-CPL)**: The translation completion from the host TA to the device ATC.

- Invalidate Request (INVAL): The invalidate request from the host TA to the device ATC.

- Invalidate Completion (INVAL-CPL): The invalidate completion from the device ATC to the host TA.

- **Page Request (PAGE)**: The page request from the device ATC to the host TA.

- **PRG Response (PGR-RSP)**: The PRG response from the host TA to the device ATC.

Table 3-10, Table 3-11, and Table 3-12 are rule summary of ATS TLP, according to [PCIe TDISP 1.0] 11.4.10, page 53.

#### Table 3-10: ATS Invalidate Request Rule Summary for TDI as Completer

| Access Control | CONFIG_UNLOCK | CONFIG_LOCK | RUN       | ERROR     |

|----------------|---------------|-------------|-----------|-----------|

| TEE-TLP        | N/A           | INVAL (V)   | INVAL (V) | INVAL (V) |

| Non-TEE-TLP    | INVAL (V)     | INVAL (V)   | INVAL (V) | INVAL (V) |

1. **INVAL** rule: Invalidation Request is allowed in TEE-TLP or Non-TEE-TLP.

2. **INVAL-CPL** rule: Invalidation Completion must use the same IDE Stream as the Invalidation Request, and **must match** the T bit value from the Invalidation Request.

#### Table 3-11: ATS Translation Request Rule Summary for TDI as Requester

| Operation   | CONFIG_UNLOCK | CONFIG_LOCK | RUN       | ERROR     |

|-------------|---------------|-------------|-----------|-----------|

| TEE-TLP     | N/A           | TRANS (X)   | TRANS (V) | TRANS (X) |

| Non-TEE-TLP | TRANS (V) **  | TRANS (X)   | TRANS (X) | TRANS (X) |

\*\* TRANS is allowed in CONFIG\_UNLOCK, if the TDI is designed to a Legacy VM.

#### Table 3-12: ATS Page Request Rule Summary for TDI as Requester

| Operation | CONFIG_UNLOCK | CONFIG_LOCK | RUN      | ERROR    |

|-----------|---------------|-------------|----------|----------|

| TEE-TLP   | N/A           | PAGE (X)    | PAGE (V) | PAGE (X) |

|  | Non-TEE-TLP | PAGE (V) ** | PAGE (X) | PAGE (X) | PAGE (X) |

|--|-------------|-------------|----------|----------|----------|

|--|-------------|-------------|----------|----------|----------|

\*\* PAGE is allowed in CONFIG\_UNLOCK, if the TDI is designed to a Legacy VM.

1. **TRANS** rule: Translation Request is only allowed with T-bit set and in RUN state. Although it is not explicit stated in TDISP specification, Translation Request is not allowed in other state (CONFIG\_UNLOCK or ERROR) or without T-bit set.

2. **TRANS-CPL** rule: Translation Completion(s) received with the T bit Clear must transition the TDI **to ERROR**.

3. **PAGE** rule: Page Request is only allowed with T-bit set and in RUN state.

4. **PGR-RSP** rule: A PRG Response must use the same IDE Stream as the corresponding Page Request and must have the T bit Set. A violation of this rule must result in the TDI transitioning **to ERROR**.

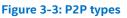

## Peer to Peer (P2P)

PCIe peer to peer (P2P) enables two PCIe device endpoints (EPs) to transfer data between each other without using host memory as a temporary storage. There are two types of P2P. See figure 3-3.

- **Direct P2P**: Two endpoints set up a dedicated P2P IDE stream with TDISP BIND\_P2P\_STREAM message. This feature requires the ATS is support and enabled for the device.

- **P2P via Root Complex**: Two endpoints set up two different IDE streams with Root Complex. If EP1 needs to send TLP to EP2, Root Complex will decrypt TLP in IDE stream 1 and encrypt it in IDE stream 2.

The TLP rule for "P2P via Root Complex" is same as the TLP rule for TEE-MMIO (Table 3-4), Non-TEE-MMIO (Table 3-5), DMA (Table 3-7).

#### 3 TEE-IO Hardware Stack

For TDX Connect compatibility, please refer to Appendix A "Access Control in TDX Connect" section.

# **TDISP Interoperability with PCIe Capabilities**

#### MSI-X

TDISP provides an optional support for TDIs to lock the MSI-X table the Pending Bit Array (PBA) in order enable trusted interrupts to TVM sending MSI-X requests using IDE-TLPs.

#### **Requirement if implemented:**

1. The device shall expose the MSI-X Capability register to the host.

2. The DSM shall lock the MSI-X table and PBA if indicated by the LOCK\_INTERFACE\_REQUEST FLAGS (Bit 2 – LOCK\_MSIX).

3. The DSM shall report the MSI-X capability message control register state in TDI Report MSI\_X\_MESSAGE\_CONTROL, according to [PCIe TDISP 1.0] Table 15 TDI Report Structure, page 37.

#### ATS

ATS is an optional feature, this document does not cover TDISP with ATS enabled devices. For more details, please refer to [PCIe TDISP 1.0].

#### **Direct P2P**

TDISP provides an optional mechanism to configure direct TDI P2P instead of using "P2P via Root Complex". This document does not cover TDISP with direct P2P enabled devices. For more details, please refer to [PCIe TDISP 1.0].

#### PASID

PASID is an optional feature that enables sharing of a single Endpoint device across multiple processes while providing each process a complete virtual address space. This document does not cover TDISP with ATS enabled devices. For more details, please refer to [PCIe TDISP 1.0].

#### LNR

LNR is deprecated in PCRE 6.0, this document does not cover TDISP with LNR enabled devices. For more details, please refer to [PCIe TDISP 1.0].

#### **3** TEE-IO Hardware Stack

#### TPH

TLP Processing Hints (TPH) is an optional feature that provides hints in Request TLP headers to facilitate optimized processing of Requests that target Memory Space. This document does not cover TDISP with TPH enabled devices. For more details, please refer to [PCIe TDISP 1.0].

For TDX Connect compatibility, please refer to Appendix A "TDISP" section.

# 4 Device Security Architecture

This chapter describes the device security architecture requirement.

# **Resource Isolation and Protection**

DSM shall implement access control and isolation mechanisms:

#### **Requirement:**

1. The device shall isolate the data for TDI from non-TDI.

2. The device shall isolate the data for one TDI from other TDIs.

3. The device shall scrub the confidential information in case of TDISP STOP\_INTERFACE, data integrity error, conventional reset, function level reset, according to [PCIe TDISP 1.0] 11.3.16. STOP\_INTERFACE\_REQUEST, 11.5.6. Data Integrity Errors, 11.4.8. Conventional Reset, 11.4.9. Function Level Reset.

4. The device should follow good practice including: securing secrets through the use of local encryption, access control, and/or other mechanisms; ensuring that secure data cannot "leak" due to errors, power management, or other operations; ensuring that secret keys are never exposed or stored in non-secure buffers; ensuring that the establishment & management of TEEs is itself secure, according to [PCIe IDE 1.0] 6.99 Implementation Note.

# **Address Translation**

Device may implement ATS.

#### **Requirement:**

1. TEE-I/O capable devices must enforce integrity of the Address Translation Cache (ATC) such that the translations provided by the Root Complex cannot be modified through untrusted accesses. [PCIe TDISP 1.0] 11.4.10, page 54.

## **Device Resource**

1. The DSM shall not support I/O resource for TVM, according to [PCIe TDISP 1.0] 11.2 TDISP Rules, page 20.

# **Device Identity and Measurement Reporting**

DSM shall implement root of trust (ROT) for device attestation.

#### **Requirement:**

1. The device shall support device identity and authentication, according to [PCIe TDISP 1.0] 11.4.1 Device Identity and Authentication, page 49.

2. The device shall support firmware and configuration measurements, according to [PCIe TDISP 1.0] 11.4.2 Firmware and Configuration Measurement, page 49.

3. The DSM shall provide ROT for storage (RTS) to provide the confidentiality for the device private key.

4. The DSM shall provide ROT for measurement (RTM) to record the measurement data at runtime.

5. The DSM shall provide ROT for reporting (RTR) to report the measurement data.

6. The device should provision the device certificate at manufacture time. A DICE device shall generate alias certificate at boot time.

7. The Device vendor should publish the reference integrity manifest (RIM) for attestation. The RIM may follow IETF CoRIM specification.

#### **Device Firmware Resilience**

Usually, the device supports firmware update. The DSM shall implement ROT for resilience.

#### **Requirement:**

1. The DSM shall provide ROT for update (RTU) for secure firmware update, including update image integrity protection and rollback protection, according to [NIST SP 800-193].

2. The DSM shall provide ROT for detection (RTD) for secure boot, including boot image integrity verification and secure version number (SVN) verification, according to [NIST SP 800-193].

3. The DSM should provide ROT for recovery (RTRec) to recover the device firmware in case of verification failure, according to [NIST SP 800-193].

#### Runtime Firmware Update

Optionally, the device may support runtime update without reset. The capability is controlled by following fields:

- **SPDM 1.2 SessionPolicy.TerminationPolicy**: Determine if runtime update will keep session alive.

- **TDISP LOCK\_INTERFACE\_REQUEST.NO\_FW\_UPDATE**: Determine if update is allowed in TDISP CONFIG\_LOCKED state.

See table 4-1.

# intel

| SPDM:             | TDISP:                | Result                                                    |

|-------------------|-----------------------|-----------------------------------------------------------|

| TerminationPolicy | NO_FW_UPDATE          |                                                           |

| 0 (No Runtime     | 0 (Allow firmware     | No Runtime Update.                                        |

| Update)           | update if TDISP is in |                                                           |

|                   | CONFIG_LOCKED         | The update will cause SPDM session                        |

|                   | state)                | termination. After update, the device will                |

|                   |                       | expect next SPDM message to be                            |

|                   |                       | GET_VERSION, and will return                              |

|                   |                       | ERROR(RequestResynch) for all other.                      |

| 0 (No Runtime     | 1 (Not allow          | No Runtime Update.                                        |

| Update)           | firmware update if    |                                                           |

|                   | TDISP is in           | Any update is not allowed if TDISP is in                  |

|                   | CONFIG_LOCKED         | CONFIG_LOCKED state. The update is                        |

|                   | state)                | allowed if TDISP is not in CONFIG_LOCKED                  |

|                   |                       | state and the update will cause SPDM session termination. |

| 1 (May support    | 0 (Allow firmware     | The device may choose to allow Runtime                    |

| Runtime Update)   | update if TDISP is in | Update regardless of the TDISP state.                     |

| Kultime Opualej   | CONFIG_LOCKED         | opuale regardless of the TDISP state.                     |

|                   | state)                | The update may keep session alive or                      |

|                   |                       | terminate. It is the device's choice based on             |

|                   |                       | the impact of the update.                                 |

| 1 (May support    | 1 (No allow           | The device may choose to allow Runtime                    |

| Runtime Update)   | firmware update if    | Update if TDISP is not in CONFIG_LOCKED                   |

|                   | TDISP is in           | state.                                                    |

|                   | CONFIG_LOCKED         |                                                           |

|                   | state)                | Any update is not allowed if TDISP is in                  |

|                   |                       | CONFIG_LOCKED state.                                      |

#### Table 4-1: Runtime Firmware Update Summary

#### **Requirement:**

1. The device shall support SPDM 1.2 SessionPolicy.TerminationPolicy = 1, to keep the SPDM session alive during runtime update.

2. The device shall keep IDE stream alive during the runtime update.

3. The device shall support TDISP LOCK\_INTERFACE\_REQUEST.NO\_FW\_UPDATE = 0, to keep TDISP alive during the runtime update.

4. The device shall support SPDM\_DIGESTS and SPDM\_CERTIFICATE command in Session.

5. The device should support SPDM 1.2 MEAS\_FRESH\_CAP to report the fresh measurement after the runtime update.

# intel

#### 4 Device Security Architecture

6. The device should support SPDM 1.2, MEASUREMENTS.Param2.content\_change detection to report the atomicity of the measurement reporting.

7. The device should support SPDM 1.2, DMTFSpecMeasurementValueType Mutable Firmware Security Version Number (SVN).

8. The DICE device shall report the certificate including the new firmware information in DiceTcbInfo, such as firmware digest and/or SVN.

## **Secure Interconnects**

The device shall support IDE based secure communication with the TSM.

#### **Requirement:**

1. The devices must support selective IDE. [PCIe TDISP 1.0] 11.4.3 Secure Interconnects, page 50.

2. The device must implement adequate security measures to prevent leakage of the encryption key at rest and in use, according to [PCIe TDISP 1.0] 11.4.3 Secure Interconnects, page 50.

# **Device Attached Memory**

A device may implement device attached memory, which is used to host the TVM data.

#### **Requirement:**

1. If device attached memory is supported, the device shall ensure the confidentiality and optionally integrity of the TVM data stored in the device attached memory, according to [PCIe TDISP 1.0] 11.4.4 Device Attached Memory, page 50.

# **TDI Security**

The device shall support TDISP protocol to manage TDI state.

#### **Requirement:**

1. The device shall follow TDI Security requirement, according to [PCIe TDISP 1.0] 11.4.5 TDI Security, page 51. The device shall support TDI state (CONFIG\_UNLOCK, CONFIG\_LOCK, RUN, ERROR) and IDE Stream state (Insecure, Secure) transition. Any configuration change that impacts the TDI security properties shall result in the TDI ERROR state and IDE Stream Insecure state.

# **Data Integrity Errors**

A device may receive a poisoned TLP on an interface in RUN.

#### **Requirement:**

1. The device shall handle data integrity error according to [PCIe TDISP 1.0] 11.4.6 Data Integrity Error, page 52. The device shall change the interface from RUN to ERROR if a poisoned TLP is received, to prevent bad data consumption and propagation. The device shall scrub and clear information in such logs and reporting registers (e.g., syndrome) that may reveal confidential data.

# **Debug Modes**

A device may support multiple debug modes or debug capabilities.

#### **Requirement:**

1. The device shall handle the debug mode, according to [PCIe TDISP 1.0] 11.4.7 Debug Modes, page 52. Debug capabilities must not affect the security of the device, and must not lead to a compromise of the confidentiality or integrity of the TVM data provided to the device.

#### **Device Debug Interface**

A device may provide debug interface to access low level data.

#### **Requirement:**

1. The device shall implement the debug interface without impacting the security properties.

2. The device should report the debug state to the host if the debug mode is enabled or a debugger is attached. The mechanism may be in SPDM measurement DeviceModeCapabilties or DiceTcbInfo flags.

# **Device Reset**

#### **Conventional Reset**

A conventional reset (cold, warm, or hot) leads to the device changing all its port registers and state machines to their initialization values, and the TDISP state of all TDIs transitions to CONFIG\_UNLOCKED.

#### **Requirement:**

1. The device shall handle the conventional reset, according to [PCIe TDISP 1.0] 11.4.8 Conventional Reset, page 53. The device shall ensure that all TVM data, IDE keys, other encryption keys (e.g., P2P links, intra-device interconnects, etc.) and SPDM session keys are

cleared and not exposed in conventional reset. The device shall reset the device measurement registers to their default values in conventional reset.

2. The device shall handle the conventional reset, according to [PCIe IDE 1.0] 6.99.8 Other IDE Rules. Any Conventional Reset to an Upstream Port or to the Bridge Function of a Downstream Port must result in all IDE Streams associated with that Function transitioning to the Insecure state, and all keys must be invalidated and rendered unreadable.

#### Function Level Reset (FLR)

A device may support function level reset.

#### **Requirement:**

1. The device shall handle the Function Level Reset (FLR), according to [PCIe TDISP 1.0] 11.4.9 Function Level Reset, page 53. The device shall ensure that all affected TDI from CONFIG\_LOCKED, RUN state to ERROR state in function level reset. As such, the host needs to issue STOP\_INTERFACE\_REQUEST request to clean up the TDI state and scrub TVM data/secrets.